# Exploiting Application Characteristics for Efficient System Support of Data-Parallel Machine Learning

Henggang Cui

May

Electrical & Computer Engineering Carnegie Mellon University Pittsburgh, PA 15213

#### Thesis Committee:

Gregory R. Ganger, Chair Phillip B. Gibbons Garth A. Gibson Eric P. Xing Derek Murray

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### Acknowledgments

I never expect that this acknowledgments section could be the toughest paragraphs to write in my Ph.D. study. There is so much that I want to thank, but, unfortunately, this type of writing is not my strength.

The most important person who made all of this come true is my advisor, Greg Ganger. I feel so fortunate to be advised by Greg because he is so smart and so helpful (especially the last week before paper deadlines). Our weekly meetings keep me always on the right track, and his jokes are funny. Many important ideas in this dissertation would not have been so well baked without his magic.

Phil Gibbons also deserves his own paragraph, because I think Phil is basically my unofficial co-advisor (at least I put his emails under the advisor label in my mailbox). Phil, Greg, and I have a one-on-two meeting every week, and Phil's feedback is equally helpful for making my work solid.

The work in this dissertation is part of the BigLearning project, and I really appreciate the feedback and suggestions from professor Garth Gibson and Eric Xing throughout my Ph.D. research work. I am also very fortunate to work with a group of wonderful collaborators in the BigLearning project. Jim Cipar and Qirong Ho were the students who started the LazyTable and Stale Synchronous Parallel project, and I have learned a lot from them. I also want to thank Aaron Harlap for having lunch with me every day. I have learned a lot from Aaron, including setting up TV antenna for the NFL games on free TV channels and playing softball.

I appreciate the insightful discussions with the BigLearning people, including Wei (David) Dai, Kevin Hsieh, Jin Kyu Kim, Jinliang Wei, and Hao Zhang, as well as the other people in the BigLearning project, including Abutalib Aghayev, Will Crichton, Andrew Chung, Dan DeCapria, Drew Gifford, John R. Klein, Dimitris Konomis, Michael Kuchnik, Lisa Lee, Seunghak Lee, Xiaodan Liang, Scott McMillan, Alex Poms, Aurick Qiao, David Shepard, Brandon Wolfe, Pengtao Xie, and Shizhen Xu.

I have been having a good time in Greg Ganger's Gang (G<sup>3</sup>), with Jim Cipar, Jesse Haber-Kucharsky, Aaron Harlap, Angela Jiang, Rajat Kateja, Elie Krevat, Michelle Mazurek, Jun Woo Park, Raja Sambasivan, Ilari Shafer, Alexey Tumanov, and Lianghong Xu, and I hope the name "G<sup>3</sup>" is still in use.

I am glad that Derek Murray joined my thesis committee. Derek was the shepherd of my GeePS work, and he has provided a lot of valuable feedback to the work in my dissertation. I did a wonderful internship at HP Labs in the summer of 2014, where I was fortunate to have Kimberly Keeton, Indrajit Roy, Krishnamurthy Viswanathan, and Haris Volos as my mentors.

My research and life has been made much easier with the help of an amazing group of administrative and technical staff at Parallel Data Lab (PDL). Karen Lindenfelser is always so helpful with all kinds of miscellaneous stuff at PDL and prepares delicious fruit and snacks for the weekly PDL meeting. Joan

Digney does a wonderful job of making posters for all my work. Jason Boles, Bill Courtright, Chuck Cranor, Chad Dougherty, Zis Economou, Mitch Franzos, and Xiaolin Zang provide wonderful technical support for the clusters that I use for my experiments.

I also want to thank my friends at PDL for the technical discussions or random chats, including David Andersen, Dana Van Aken, George Amvrosiadis, Joy Arulraj, Rachata Ausavarungnirun, Ben Blum, Sol Boucher, Christopher Canel, Lei Cao, Kevin Chang, Debanshu Das, Utsav Drolia, Chris Fallin, Bin Fan, Kayvon Fatahalian, Nitin Gupta, Kiryong Ha, Mor Harchol-Balter, Junchen Jiang, Wesley Jin, Anuj Kalia, Michael Kaminsky, Atsushi Kawamura, Mike Kozuch, Akira Kuroda, Conglong Li, Mu Li, Hyeontaek Lim, Yixin Luo, Lin Ma, Priya Narasimhan, Andy Pavlo, Kai Ren, Majd Sakr, Vivek Seshadri, Alex Smola, Joshua Tan, Thomas Tauber-Marshall, Iulian Moraru, Jiri Simsa, Nandita Vijaykumar, Lin Xiao, Hongyi Xin, Huanchen Zhang, Michael (Tieying) Zhang, Jie Zhang, Qing Zheng, Dong Zhou, and Timothy Zhu.

CIC 2nd floor is a great working environment, except for being freezing in the summer, and I have many good friends here, including Tiffany (Youzhi) Bao, Chen Chen, Yanli Li, Jiaqi Liu, Mahmood Sharif, Janos Szurdi, Miao Yu, and Tianlong Yu.

I also want to thank the members and companies of the PDL Consortium (including Broadcom, Citadel, Dell EMC, Google, Hewlett-Packard Labs, Hitachi, Intel Corporation, Microsoft Research, MongoDB, NetApp, Oracle Corporation, Samsung Information Systems America, Seagate Technology, Tintri, Two Sigma, Toshiba, Uber, Veritas, and Western Digital) for their interest, insights, feedback, and support. The work in this dissertation is supported in part by Intel as part of the Intel Science and Technology Center for Cloud Computing (ISTC-CC), National Science Foundation under awards CNS-1042537 and CNS-1042543 (PRObE).

Finally, I want to thank my wife for accompanying me through the tough times, my parents for always backing me up. They have made all of this happen.

#### Abstract

Large scale machine learning has many characteristics that can be exploited in the system designs to improve its efficiency. This dissertation demonstrates that the characteristics of the ML computations can be exploited in the design and implementation of parameter server systems, to greatly improve the efficiency by an order of magnitude or more. We support this thesis statement with three case study systems, IterStore, GeePS, and MLtuner. IterStore is an optimized parameter server system design that exploits the repeated data access pattern characteristic of ML computations. The designed optimizations allow IterStore to reduce the total run time of our ML benchmarks by up to 50×. GeePS is a parameter server that is specialized for deep learning on distributed GPUs. By exploiting the layer-by-layer data access and computation pattern of deep learning, GeePS provides almost linear scalability from single-machine baselines (13× more training throughput with 16 machines), and also supports neural networks that do not fit in GPU memory. MLtuner is a system for automatically tuning the training tunables of ML tasks. It exploits the characteristic that the best tunable settings can often be decided quickly with just a short trial time. By making use of optimization-guided online trial-and-error, MLtuner can robustly find and re-tune tunable settings for a variety of machine learning applications, including image classification, video classification, and matrix factorization, and is over an order of magnitude faster than traditional hyperparameter tuning approaches.

# Contents

| 1 | Intr | roducti | ion 1                                                                                                                     |  |  |  |  |

|---|------|---------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   | 1.1  | Thesis  | s statement                                                                                                               |  |  |  |  |

|   | 1.2  | Contri  | butions                                                                                                                   |  |  |  |  |

|   | 1.3  | Outlin  | ue                                                                                                                        |  |  |  |  |

| 2 | Bac  | kgroui  | nd: Data-Parallel ML and Parameter Servers 5                                                                              |  |  |  |  |

|   | 2.1  | Data-   | parallel machine learning                                                                                                 |  |  |  |  |

|   | 2.2  | Consis  | stency models for data-parallel ML                                                                                        |  |  |  |  |

|   | 2.3  | Param   | neter server architecture                                                                                                 |  |  |  |  |

|   | 2.4  | Exam    | ple ML applications and algorithms                                                                                        |  |  |  |  |

|   |      | 2.4.1   | Matrix factorization for movie recommendation                                                                             |  |  |  |  |

|   |      | 2.4.2   | Deep learning                                                                                                             |  |  |  |  |

|   |      | 2.4.3   | Latent Dirichlet allocation (LDA) for topic modeling                                                                      |  |  |  |  |

|   |      | 2.4.4   | PageRank                                                                                                                  |  |  |  |  |

| 3 | Iter | Store:  | Exploiting Iterativeness for Efficient Parallel ML 15                                                                     |  |  |  |  |

|   | 3.1  | 1 0     |                                                                                                                           |  |  |  |  |

|   | 3.2  |         | iting iterative-ness for performance                                                                                      |  |  |  |  |

|   |      | 3.2.1   | Obtaining per-iteration access sequence                                                                                   |  |  |  |  |

|   |      | 3.2.2   | Exploiting access information                                                                                             |  |  |  |  |

|   |      | 3.2.3   | Limitations                                                                                                               |  |  |  |  |

|   | 3.3  | Implei  | mentation                                                                                                                 |  |  |  |  |

|   |      | 3.3.1   | System architecture                                                                                                       |  |  |  |  |

|   |      | 3.3.2   | Access information gathering                                                                                              |  |  |  |  |

|   |      | 3.3.3   | Efficient data structures                                                                                                 |  |  |  |  |

|   |      | 3.3.4   | Data placement across machines                                                                                            |  |  |  |  |

|   |      | 3.3.5   | Data placement inside a machine                                                                                           |  |  |  |  |

|   |      | 3.3.6   | Contention and locality-aware thread caches                                                                               |  |  |  |  |

|   |      | 3.3.7   | Prefetching                                                                                                               |  |  |  |  |

|   | 3.4  | Evalua  | ation $\dots \dots \dots$ |  |  |  |  |

|   |      | 3.4.1   | Experimental setup                                                                                                        |  |  |  |  |

|   |      | 3.4.2   | Overall performance                                                                                                       |  |  |  |  |

|   |      | 3.4.3   | Optimization effectiveness break down                                                                                     |  |  |  |  |

|   |      | 3 / /   | Contention and locality aware eaching                                                                                     |  |  |  |  |

|   |     | 3.4.5           | Pipelined prefetching                                        | 31 |

|---|-----|-----------------|--------------------------------------------------------------|----|

|   |     | 3.4.6           | Inaccurate information                                       | 32 |

|   |     | 3.4.7           | Comparison with single thread baselines                      | 33 |

|   | 3.5 | Additi          | ional Related Work                                           | 34 |

|   |     |                 |                                                              |    |

| 4 |     |                 | xploiting Layered Computation for Efficient Deep Learning on |    |

|   |     |                 | ed GPUs                                                      | 35 |

|   | 4.1 |                 | performance deep learning                                    | 36 |

|   |     | 4.1.1           | Deep learning using GPUs                                     | 36 |

|   |     | 4.1.2           | Scaling distributed GPU ML with a parameter server           | 37 |

|   | 4.2 | GPU-s           | specialized parameter server design                          | 38 |

|   |     | 4.2.1           | Maintaining the parameter cache in GPU memory                | 39 |

|   |     | 4.2.2           | Pre-built indexes and batch operations                       | 40 |

|   |     | 4.2.3           | Managing limited GPU device memory                           | 40 |

|   |     | 4.2.4           | Eschewing asynchrony                                         | 42 |

|   | 4.3 | GeePS           | Simplementation                                              | 42 |

|   |     | 4.3.1           | GeePS data model and API                                     | 42 |

|   |     | 4.3.2           | GeePS architecture                                           | 43 |

|   |     | 4.3.3           | Parallelizing batched access                                 | 45 |

|   |     | 4.3.4           | GPU memory management                                        | 46 |

|   | 4.4 | Evalua          | ation                                                        | 48 |

|   |     | 4.4.1           | Experimental setup                                           | 48 |

|   |     | 4.4.2           | Scaling deep learning with GeePS                             | 50 |

|   |     | 4.4.3           | Dealing with limited GPU memory                              | 53 |

|   |     | 4.4.4           | The effects of looser synchronization                        | 56 |

|   | 4.5 |                 | ional related work                                           | 58 |

|   |     |                 |                                                              |    |

| 5 | ML  | tuner:          | Exploiting Quick Tunable Decision for Automatic ML Tuning    | 61 |

|   | 5.1 | Backg           | round and related work                                       | 62 |

|   |     | 5.1.1           | Machine learning tunables                                    | 62 |

|   |     | 5.1.2           | Related work on machine learning tuning                      | 63 |

|   | 5.2 | MLtur           | ner: more efficient automatic tuning                         | 64 |

|   |     | 5.2.1           | MLtuner overview                                             | 64 |

|   |     | 5.2.2           | Trying and evaluating tunable settings                       | 65 |

|   |     | 5.2.3           | Tunable tuning procedure                                     | 66 |

|   |     | 5.2.4           | Assumptions and limitations                                  | 66 |

|   | 5.3 | MLtur           | ner implementation details                                   | 67 |

|   |     | 5.3.1           | Measuring convergence speed                                  | 67 |

|   |     | 5.3.2           | Deciding tunable trial time                                  | 68 |

|   |     | 5.3.3           | Tunable searcher                                             | 68 |

|   |     | 5.3.4           | Re-tuning tunables during training                           | 69 |

|   |     | 5.3.5           | Training system interface                                    | 70 |

|   |     | 5.3.6           | Training system modifications                                | 71 |

|   | 5 4 | 5.5.0<br>Evalua | • •                                                          | 79 |

|   | 4   | 17/201112       |                                                              | /  |

|   |     | 5.4.1  | Experimental setup                                      | 72 |

|---|-----|--------|---------------------------------------------------------|----|

|   |     | 5.4.2  | MLtuner vs. state-of-the-art auto-tuning approaches     | 75 |

|   |     | 5.4.3  | Tuning initial LR for adaptive LR algorithms            | 77 |

|   |     | 5.4.4  | MLtuner vs. idealized manually-tuned settings           | 79 |

|   |     | 5.4.5  | Robustness to suboptimal initial settings               | 81 |

|   |     | 5.4.6  | Scalability with more tunables                          | 82 |

| 6 | Con | clusio | n and Future Directions                                 | 83 |

|   | 6.1 | Conclu | usion                                                   | 83 |

|   | 6.2 | Future | e Directions                                            | 84 |

|   |     | 6.2.1  | Detecting and adapting to access pattern changes        | 84 |

|   |     | 6.2.2  | Time-aware iterativeness exploitation                   | 84 |

|   |     | 6.2.3  | Exploiting layer heterogeneity for deep learning        | 84 |

|   |     | 6.2.4  | Combing MLtuner with non-convex optimization techniques | 85 |

|   |     | 6.2.5  | Extending MLtuner to model hyperparameter searching     | 85 |

|   | 6.3 | More : | Future Directions                                       | 85 |

|   |     | 6.3.1  | Dynamic data and/or models                              | 86 |

|   |     | 6.3.2  | Systems for both model training and model serving       | 86 |

# List of Figures

| 2.1        | Bulk Synchronous Parallel (BSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2<br>2.3 | Stale Synchronous Parallel (SSP), with a slack of one clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7  |

| 2.3        | Parallel ML with parameter server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 |

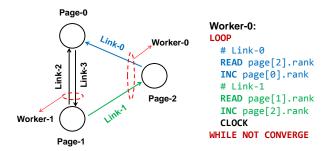

| 3.1        | Iterativeness in PageRank. The graph contains three pages and four links. Each of the two workers is assigned with two links. In every iteration, each worker goes through its assigned links. For each link, the worker reads the rank of the source page and updates the rank of the destination page. The same sequence of accesses repeats every iteration                                                                                                                                                                      | 16 |

| 3.2        | Two ways of collecting access information. The left-most pseudo-code illustrates a simple iterative ML program flow, for the case where there is a Clock after each iteration. The middle pseudo-code adds code for informing the parameter server of the start and end of the first iteration, so that it can record the access pattern and then reorganize (during ps.FinishGather) to exploit it. The right-most pseudo-code adds a virtual iteration to do the same, re-using the same DoIteration code as the real processing. | 18 |

| 3.3        | IterStore with two partitions, running on two machines with two application                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 0.0        | threads each.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21 |

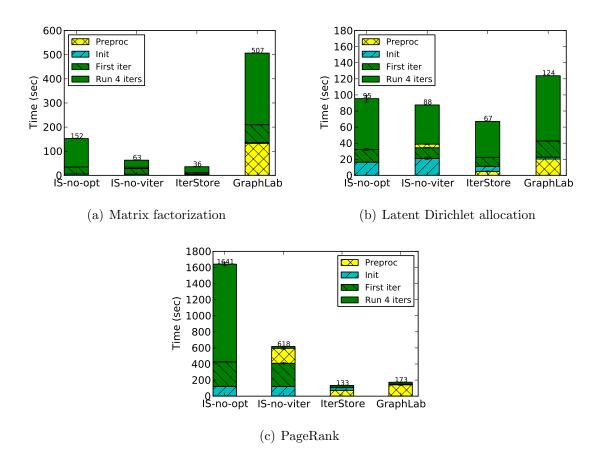

| 3.4        | Performance comparison, running 5 iterations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27 |

| 3.5        | Performance comparison, running 100 iterations. The "IS-no-opt" bar in the PageRank figure is cut off at 2000 sec, because it's well over an order of                                                                                                                                                                                                                                                                                                                                                                               |    |

|            | magnitude worse than the other three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

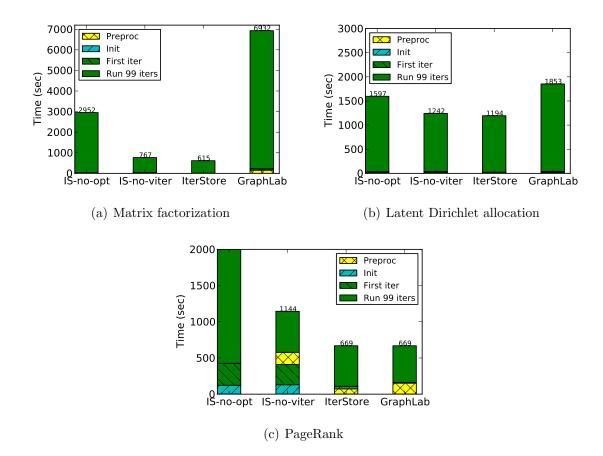

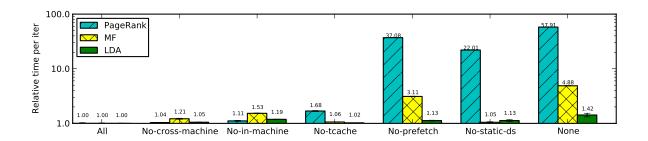

| 3.6        | Turn on one of the optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29 |

| 3.7        | Turn off one of the optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29 |

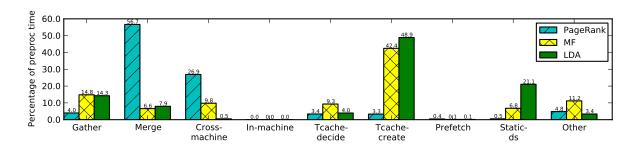

| 3.8        | Preprocessing time break down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

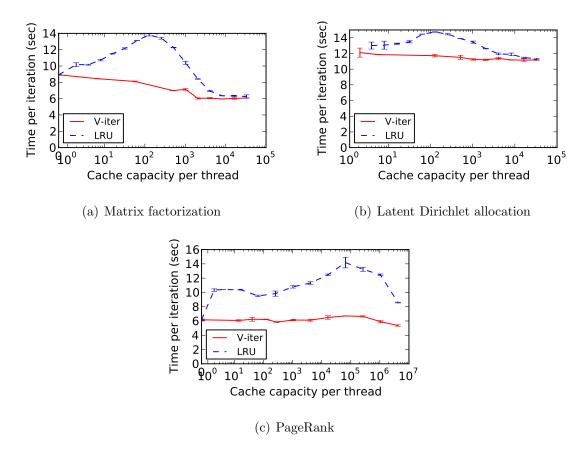

| 3.9        | Comparing IterStore's static cache to LRU, varying the cache size (log scale).                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

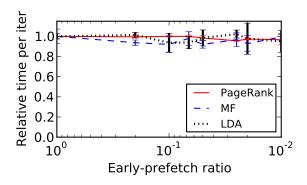

| 3.10       | Pipelined prefetching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32 |

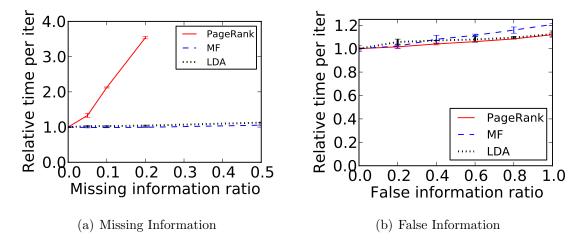

| 3.11       | Influence of inaccurate information. Data point "missing information ratio is 0.2%" means that, the number of the missing unreported accesses is 20% of the number of the actual accesses (i.e., report 20% less). Data point "false information ratio is 0.2%" means that, the number of the false accesses is                                                                                                                                                                                                                     |    |

|            | 20% of the number of the actual accesses (i.e., report $20%$ more)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |

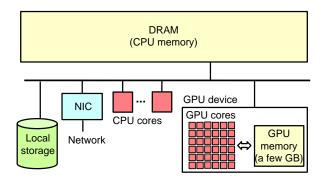

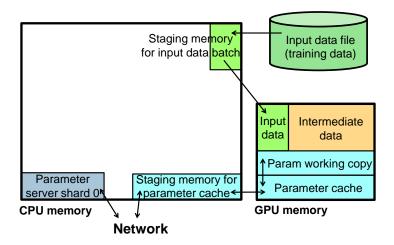

| 4.1<br>4.2 | A machine with a GPU device                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

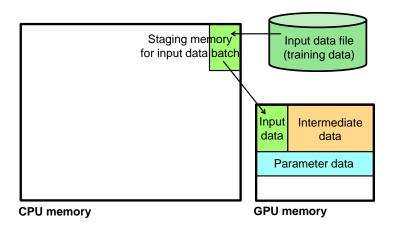

| 4.3        | Distributed ML on GPUs using a CPU-based parameter server. The right                                                                                        |

| 1.0        | side of the picture is much like the single-GPU illustration in Figure 4.2. But, a                                                                          |

|            | parameter server shard and client-side parameter cache are added to the CPU                                                                                 |

|            | memory, and the parameter data originally only in the GPU memory is replaced in                                                                             |

|            | GPU memory by a local working copy of the parameter data. Parameter updates                                                                                 |

|            | must be moved between CPU memory and GPU memory, in both directions,                                                                                        |

|            | which requires an additional application-level staging area since the CPU-based                                                                             |

|            | parameter server is unaware of the separate memories                                                                                                        |

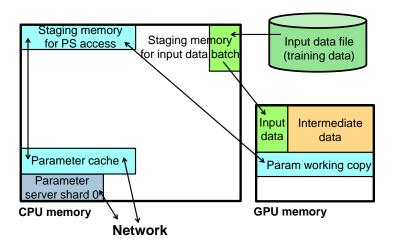

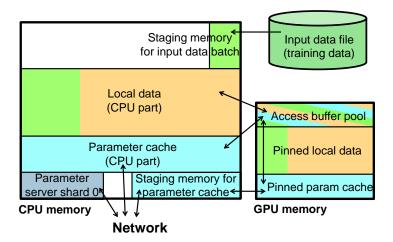

| 4.4        | Parameter cache in GPU memory. In addition to the movement of the parameter                                                                                 |

| 4.4        | cache box from CPU memory to GPU memory, this illustration differs from                                                                                     |

|            | Figure 4.3 in that the associated staging memory is now inside the parameter                                                                                |

|            | server library. It is used for staging updates between the network and the parameter                                                                        |

|            | cache, rather than between the parameter cache and the GPU portion of the                                                                                   |

|            | application                                                                                                                                                 |

| 4.5        | Parameter cache and local data partitioned across CPU and GPU memories.                                                                                     |

| 4.0        | When all parameter and local data (input data and intermediate data) cannot                                                                                 |

|            | fit within GPU memory, our parameter server can use CPU memory to hold the                                                                                  |

|            | excess. Whatever amount fits can be pinned in GPU memory, while the remainder                                                                               |

|            | is transferred to and from buffers that the application can use, as needed 4.                                                                               |

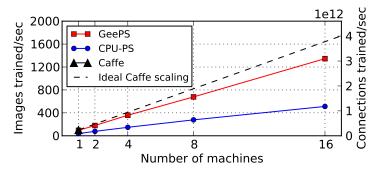

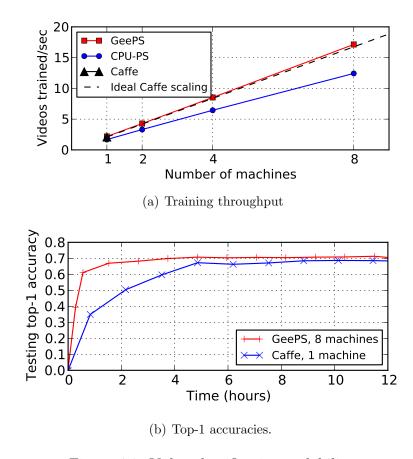

| 4.6        | Image classification throughput scalability. Both GeePS and CPU-PS run in                                                                                   |

| 4.0        | the BSP mode                                                                                                                                                |

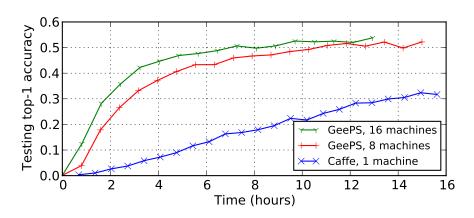

| 4.7        | Image classification top-1 accuracies                                                                                                                       |

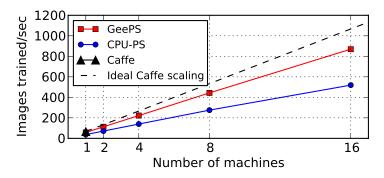

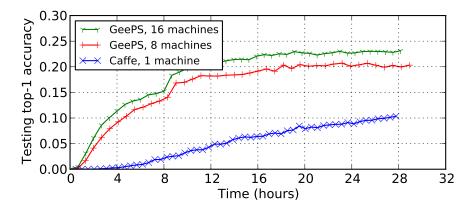

| 4.8        | Video classification scalability                                                                                                                            |

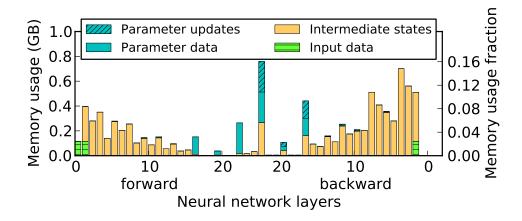

| 4.9        | ·                                                                                                                                                           |

|            |                                                                                                                                                             |

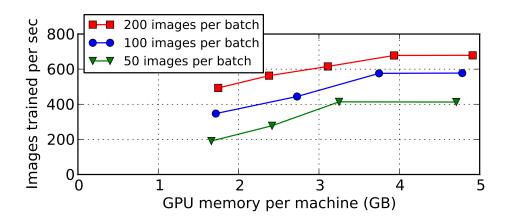

| 4.10       | Throughput of AdamLike model on ImageNet22K dataset with different                                                                                          |

| 111        | GPU memory budgets                                                                                                                                          |

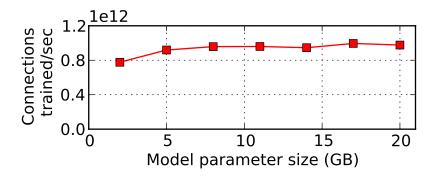

| 4.11       | Training throughput on very large models. Note that the number of connections                                                                               |

|            | increases linearly with model size, so the per-image training time grows with model size because the per-connection training time stays relatively constant |

| 4 10       |                                                                                                                                                             |

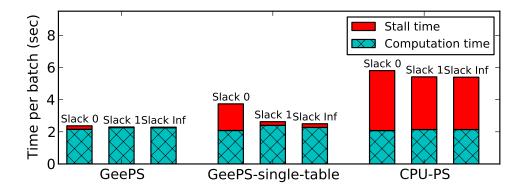

| 4.12       | Data-parallel per-mini-batch training time for AdamLike model under different configurations. We refer to "stell time" as any part of the mustime when      |

|            | ent configurations. We refer to "stall time" as any part of the runtime when                                                                                |

| 4 1 9      | GPUs are not doing computations                                                                                                                             |

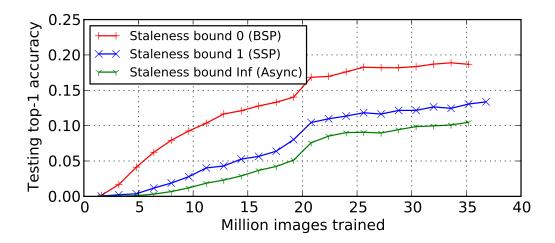

| 4.13       | AdamLike model top-1 accuracy as a function of the number of training                                                                                       |

|            | images processed, for BSP, SSP with slack 1, and Async                                                                                                      |

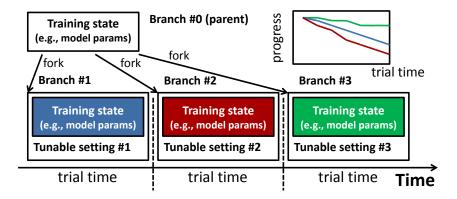

| 5.1        | Trying tunable settings in training branches. The red branch with tunable                                                                                   |

| 9          | setting #2 has the fastest convergence speed                                                                                                                |

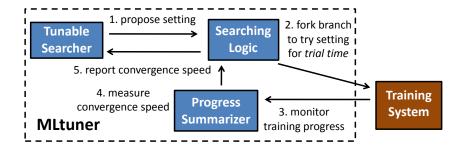

| 5.2        | MLtuner tuning procedure                                                                                                                                    |

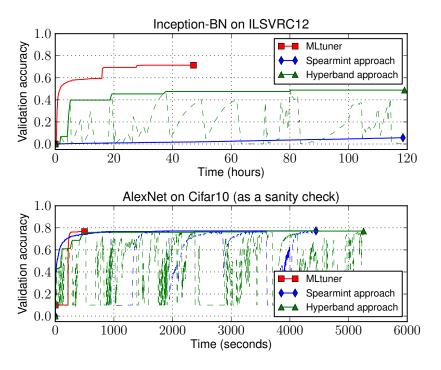

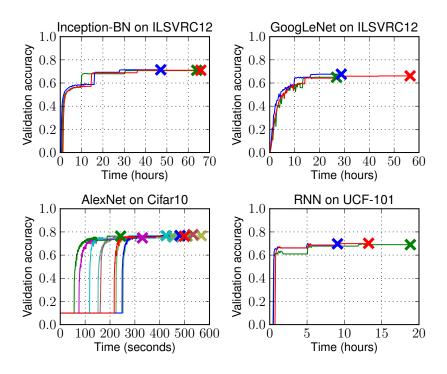

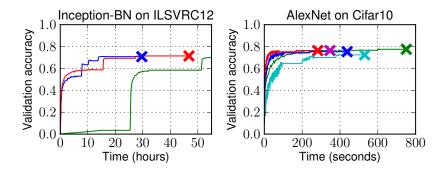

| 5.3        | Runtime and accuracies of MLtuner and the state-of-the-art approaches.                                                                                      |

|            | For Spearmint and Hyperband, the dashed curves show the accuracies of each                                                                                  |

|            | configuration tried, and the bold curves show the maximum accuracies achieved                                                                               |

|            | over time                                                                                                                                                   |

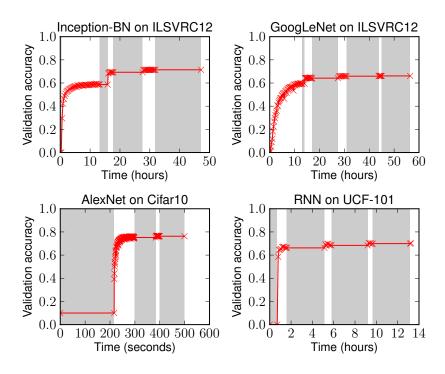

| 5.4  | MLtuner tuning/re-tuning behavior on four deep learning benchmarks. The             |    |

|------|-------------------------------------------------------------------------------------|----|

|      | markers represent the validation accuracies measured at each epoch. The shaded      |    |

|      | time ranges are when MLtuner tunes/re-tunes tunables                                | 77 |

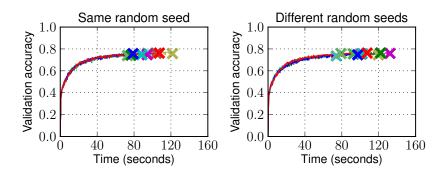

| 5.5  | MLtuner results of multiple runs. The larger "x" markers mark the end of each       |    |

|      | run. The runs with the median performance are shown as the red curves in this       |    |

|      | figure and as the "MLtuner" curves in the other figures                             | 78 |

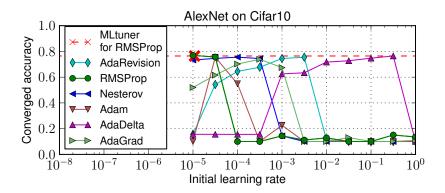

| 5.6  | Converged validation accuracies when using different initial learning rates.        |    |

|      | The "x" marker marks the LR picked by MLtuner for RMSProp                           | 79 |

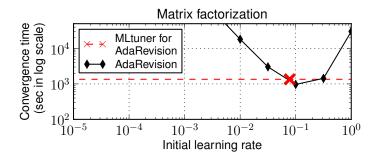

| 5.7  | Convergence time when using different initial learning rates. The "x" marker        |    |

|      | marks the LR picked by MLtuner                                                      | 79 |

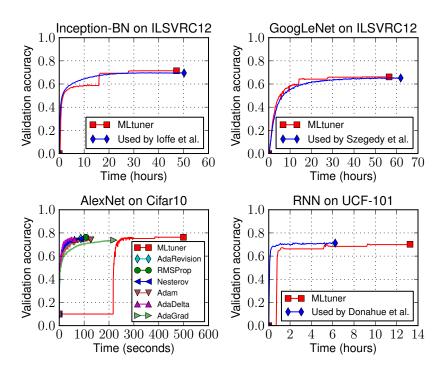

| 5.8  | MLtuner compared with manually tuned settings. For comparison purpose,              |    |

|      | we have run the manually tuned settings (except for Cifar10) for long enough to     |    |

|      | ensure that their accuracies will not increase any more, rather than stopping them  |    |

|      | according to the convergence condition                                              | 80 |

| 5.9  | Performance for multiple training runs of AlexNet on Cifar10 with RMSProp           |    |

|      | and the optimal initial LR setting                                                  | 81 |

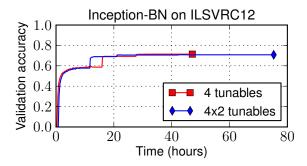

| 5.10 | MLtuner performance with hard-coded initial tunable settings. The red               |    |

|      | curves used the tuned initial settings, and the other curves used randomly selected |    |

|      | suboptimal initial settings.                                                        | 82 |

| 5.11 | MLtuner performance with more tunables                                              | 82 |

# List of Tables

| 3.1 | Benchmarks characteristics                                                 | 29 |

|-----|----------------------------------------------------------------------------|----|

| 3.2 | Time per iteration comparison of single-threaded non-distributed implemen- |    |

|     | tations using one machine versus IterStore using 8 machines, 512 cores and |    |

|     | 512 threads                                                                | 33 |

| 4.1 | GeePS API calls used for access to parameter data and GeePS-managed        |    |

|     | local data                                                                 | 40 |

| 4.2 | Model training configurations                                              | 50 |

| 5.1 | MLtuner message signatures                                                 | 70 |

| 5.2 | Applications used in the experiments. They have distinct characteristics   | 72 |

| 5.3 | Tunable setups in the experiments                                          | 74 |

# Chapter 1

# Introduction

Large scale machine learning has emerged as a primary computing activity in business, science, and services, attempting to extract insight from quantities of observation data. A machine learning task assumes a particular mathematical *model* will describe the observed training data and use an algorithm to identify *model parameter* values that make it fit the input data most closely. Depending on the application, such models can expose relationships among data items (e.g., for grouping documents into topics), predict outcomes for new data items based on selected characteristics (e.g., for classification tasks and recommendation systems), correlate effects with causes (e.g., for genomic analyses of diseases), and so on.

We focus on one major subset of these ML tasks that we refer to as iterative data-parallel machine learning. Examples include deep learning for image and video classification, matrix factorization for movie recommendation, and topic modeling. For those ML tasks, the ML algorithm (such as SGD) starts with some initial parameter value guesses, and then performs a number of *iterations* to refine them. Each iteration evaluates each input datum, one by one, against current model parameters and adjusts parameters to better fit that datum. The expensive computation required often makes it desirable to run these ML tasks distributedly on a cluster of machines. We focus on a *data-parallel* approach of parallelizing such tasks, in which the training data is partitioned among workers, and the workers iteratively make changes to the shared model parameter data, based on their local training data.

While other designs can be used, an increasingly popular design for maintaining the distributed shared parameter data is to use a so-called *parameter server* architecture [4, 73, 59, 29, 20, 28, 27, 25, 92]. The parameter server manages the shared parameter data for the application and takes care of all the distributed system details, such as propagating parameter updates and synchronizing parameter data among workers. Designing a parameter server that can scale efficiently is challenging. The challenges include overcoming the overhead of communication and synchronization, and supporting specialized hardware, such as GPUs.

## 1.1 Thesis statement

This dissertation describes our parameter system designs that address those challenges by exploiting the characteristics of ML computations. In particular, we make the following thesis statement:

The characteristics of large-scale data-parallel machine learning computations can be exploited in the implementation of a parameter server to increase their efficiency by an order of magnitude or more.

To support this thesis statement, we will show three case studies of specializing parameter server designs that exploit different characteristics of ML computations.

- IterStore: exploiting repeated parameter data access pattern (Chapter 3). Many iterative ML algorithms have the property that the same (or nearly the same) sequence of accesses is applied to the parameter server every iteration. This repeating sequence can be exploited to improve the performance of parameter servers. We designed a virtual iteration method to collect this repeating access sequence from the application, and employed five parameter server specializations using the collected information, including prefetching, contiguous marshalling-free data storage, locality and NUMA-aware data placement, and specialized caching policy. Our experiments show that these specializations greatly reduce the total run time of our application benchmarks by up to 50×.

- GeePS: exploiting layer-by-layer computation of deep learning (Chapter 4). Deep neural networks are often trained using GPUs, but scaling GPU applications on multiple machines is challenging, because of the limited GPU memory size and expensive data movement overheads between GPU and CPU memory. We have designed a parameter server system, called GeePS, that is specialized for GPU deep learning applications. We identify an important characteristic of the deep learning application that their data access and computation is performed layer-by-layer. By exploiting this characteristic, GeePS is able to hide communication latency from the application, and support neural networks that do not fit in GPU memory, by swapping data from/to CPU memory in the background. We have linked GeePS with Caffe, a state-of-art single-machine deep learning system, and our experiments show that GeePS provides almost linear scalability from single-machine Caffe (13× more training throughput with 16 machines).

- MLtuner: exploiting quick decision and dynamism of training tunable selection (Chapter 5). Training a machine learning model involves the selection and tuning of many training tunables, such as the mini-batch size, learning rate, and synchronization policy. The best setting of these tunables depends on many factors, such as the problem, the dataset, and the hardware environment, and is often hard to decide offline. Moreover, the best settings often change during the training. A bad choice of the tunables can make the model converge very slowly, converge to suboptimal solution, or even not converge. We designed a system, called MLtuner, that is able to automatically select and tune the training tunables for machine learning systems. It can be integrated with existing parameter server systems, such

as IterStore and GeePS. MLtuner exploit the characteristics of the ML tasks that the best tunable setting can often be decided quickly, with a short trial time. It uses efficient snapshotting and optimization-guided online trial-and-error to find good initial tunable settings as well as to re-tune settings during training. Our experiments with five real ML tasks, including deep learning and matrix factorization, show that MLtuner can robustly find and re-tune tunable settings for them, and is over an order of magnitude faster than traditional hyperparameter tuning approaches.

### 1.2 Contributions

This dissertation makes the following key contributions.

#### IterStore:

- It identifies iterative-ness as a property of many data-parallel ML applications that can and should be exploited to improve efficiency significantly.

- It describes and evaluates a broad collection of specializations that exploit iterativeness effectively, showing their overall and individual values for several real ML applications.

- It describes and evaluates the concept of a virtual iteration and compares it with detection of patterns during the first iteration.

#### GeePS:

- It describes the first GPU-specialized parameter server design and the changes needed to achieve efficient data-parallel multi-machine deep learning with GPUs.

- It reports on large-scale experiments showing that GeePS indeed supports scalable data parallel execution via a parameter server, in contrast to previous expectations.

- It introduces new parameter server support for enabling such data-parallel deep learning on GPUs even when models are too big to fit in GPU memory, by explicitly managing GPU memory as a cache for parameters and intermediate layer state.

#### MLtuner:

- It introduces the first approach for automatically tuning the multiple tunables associated with nearly any ML application within the context of a single execution of that application.

- It describes a tool (MLtuner) that implements the approach, overcoming various challenges, and how MLtuner was integrated with two different ML training systems.

- It presents results from experiments with real ML applications, demonstrating the efficacy of this new approach in removing the black art of tuning from ML application training.

## 1.3 Outline

The remainder of this dissertation is organized as follows. Chapter 2 motivates our works with more background on data-parallel machine learning, the parameter server architecture,

and some popular machine learning applications. Chapter 3 describes IterStore [27], our parameter server design that exploits the iterativeness characteristic of ML computations. Chapter 4 describes GeePS [28], our parameter server design that exploits the layer-by-layer computation pattern of GPU-based deep learning applications. Chapter 5 describes MLtuner, a system for automatically picking and tuning training tunables. Chapter 6 concludes the dissertation and discusses future research directions.

# Chapter 2

# Background: Data-Parallel ML and Parameter Servers

This section describes some additional background of our work, including data-parallel machine learning, consistency models, the parameter server architecture, and popular ML application benchmarks.

# 2.1 Data-parallel machine learning

The goal of a ML task is to train a ML model on training (input) data, so that the trained model can be used to make predictions on unseen data. A model has trainable model parameters, and the ML task tries to determine the values of these model parameters that best fit the training data. The fitness error of the set of model parameters to the training data is defined mathematically with an objective function, and the current value of the objective function is often called the objective value or training loss. Thus, the machine learning problem is an optimization problem, whose goal is to minimize the objective function.

The ML task often optimizes the objective function with an iterative convergent algorithm. For example, with the gradient descent algorithm, the model parameters are first initialized to some random values, and in every step, the gradient descent algorithm calculates the gradient of the objective function, w.r.t. the model parameters. The model parameter change will be the opposite direction of the gradient (if we want to minimize the objective function), multiplied by a *learning rate*. The algorithm will repeat the above steps for multiple *iterations*, until the model converges. For large-scale machine learning problems, where the size of the training data is large, people often use the stochastic gradient descent (SGD) algorithm, where in each iteration, the gradients are calculated on just one batch of the training data, rather than all the training data.

To speed up ML tasks, people often distribute the ML computations across a cluster of machines. The *data-parallel* approach is a popular approach of doing that, where the training data is partitioned across multiple ML workers on different machines. Each ML worker keeps a local copy of the model parameters and computes model gradients based

on their local model parameter copy and training data partition. The ML workers will propagate the computed model gradients and refresh their model parameter copies every *clock*, which is often logically defined as some unit of work (e.g., every training data batch).

# 2.2 Consistency models for data-parallel ML

When the model is trained in the distributed manner, the ML workers will have temporarily inconsistent model parameter copies, causing *data staleness errors* [42, 25]. To guarantee model convergence, it is usually necessary to enforce some *consistency model* that bounds the data staleness in some way. There are generally three types of consistency models to be considered.

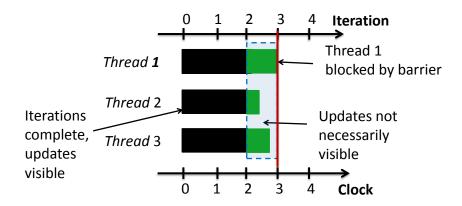

Figure 2.1: Bulk Synchronous Parallel (BSP).

The Bulk Synchronous Parallel (BSP) model, as illustrated in Figure 2.1, requires that all workers must see the parameter updates from all other workers from all previous clocks, before proceeding to the next clock. BSP guarantees the workers a fresh view of the model parameters every clock, which is often defined as one iteration. The potential problem with the BSP model is that the time waiting for communication might block the computation, and moreover, a slower worker (i.e., a straggler) can slow down the whole computation. At the other end of the spectrum, is the Asynchrony model [74, 20], where the workers never wait for each other, and the amount of data staleness error depends on the best-effort communication throughput and latency. The potential problem of the Asynchrony model is that the model might need more iterations to converge or even diverge.

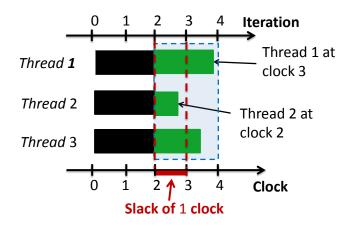

The Stale Synchronous Parallel (SSP) model [42, 25] is a middle ground between BSP and Asynchrony. It provides a looser but still bounded data staleness guarantee. As is illustrated in Figure 2.2, SSP allows the fastest worker to be ahead of the slowest worker by up to slack clocks. For example, with a slack of s, a worker at clock t is guaranteed to see all updates from clocks 1 to t - s - 1, and it may see (not guaranteed) the updates after clock t - s - 1. SSP generalizes BSP and Asynchrony, making BSP a special case with zero slack and Asynchrony a special case with infinite slack. By introducing this slack parameter, SSP allows people to explicitly balance data freshness and system throughput.

Figure 2.2: Stale Synchronous Parallel (SSP), with a slack of one clock.

### 2.3 Parameter server architecture

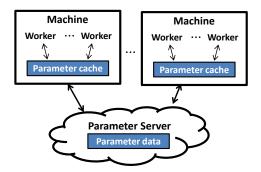

Figure 2.3: Parallel ML with parameter server.

For data-parallel ML, the shared model parameters are often managed with a parameter server system [59, 25, 28, 92, 27, 20, 29, 4, 73]. Figure 2.3 illustrates the basic parameter server architecture. The ML application launches multiple workers, and each of them process their assigned training data, and communicates with the parameter server to read and update the shared model parameter data.

**Key-value interface.** The parameter server is essentially a distributed key-value store and provides a simple key-value interface for the ML application to to read and update the shared model parameters, and synchronize their progress. This interface usually includes:

- Read: reads the parameter data. To support the Stale Synchronous Parallel model, some parameter servers (e.g., [25, 92]) allows the application to specify the slack parameter for each Read operation.

- Update: updates the parameter data by *delta*. The user will need to define an update function to merge the parameter update *delta* with the current parameter data. The update function is often required to be associative and commutative, so that the

updates from different ML workers can be applied in any order. For most of our applications, this update function is simply an addition-assignment operation (+ =).

• Clock: signals the completion of one clock of work. Each clock of work is usually logically defined as processing one batch of the training data.

Sharding. The parameter server is usually a distributed key-value store, and the parameter data is sharded across multiple parameter server shards. While Figure 2.3 illustrates the parameter server as separate from the machines executing ML workers, the state-of-art parameter server systems (e.g., [25, 92, 27, 28]) often places the shards across the same machines as the ML workers. This approach avoids dedicating extra machines to run the parameter server and allows some degree of data locality to be explored, as is shown in our IterStore work described in Chapter 3.

Caching. To avoid constant remote communication, a parameter server system often includes client-side caches that serve most operations locally. For example, when the application calls an Update operation, the parameter updates will be first coalesced in the update caches, and will then be propagated to the parameter servers when the Clock operation is called.

Consistency guarantees. The parameter server often supports the Staleness Synchronous Parallel model, which generalizes BSP and Asynchrony. It maintains the specified data staleness bound by attaching a data age field with each parameter data entry. When a parameter data entry has a data age of t, it means that the data includes all the parameter updates from all workers up to clock t. The parameter server will block the Read operations, when the data is not fresh enough. For example, when an application worker at clock T reads the parameter data with a slack of s clocks, the Read operation will be blocked, if the parameter data age is less than T - s - 1.

Fault tolerance. Because training an ML model is often an offline task, which requires high throughput rather than high availability from the parameter server, most of the state-of-art parameter sever implementations (e.g., [25, 92, 27, 28]) do not replicate the parameter data. Instead, they handle the fault tolerance by checkpointing (e.g., taking a checkpoint every hour). To make a consistent checkpoint, the client can just broadcast the checkpointing command to all the parameter server shards, telling them at which clock the checkpoint needs to be made, and the parameter server shards will take the checkpoint independently when they reach that clock.

# 2.4 Example ML applications and algorithms

This section describes the popular ML applications that are frequently used in our work, including their algorithms, and how they are parallelized with parameter server systems.

#### 2.4.1 Matrix factorization for movie recommendation

Matrix factorization is a technique commonly used in recommendation systems, such as recommending movies to users on Netflix (a.k.a. collaborative filtering). The key idea is to discover latent interactions between the two entities (e.g., users and movies) via

matrix factorization. Given a partially filled rating matrix X of size  $N \times M$ , where each known entry (i,j) is user i's rating of movie j, matrix factorization factorizes X into two lower-ranked factor matrices L with size  $N \times K$  and R with size  $K \times M$  (usually K << N and K << M), such that their product can be used to predict the missing entries of X (i.e.,  $X \approx L \cdot R$ ). For this application, the known entries of X is the training data, and X and X are the model parameters.

For this application, the goal is to minimize the objective function, which is often defined as the squared difference between each known entry  $X_{ij}$  and its prediction  $L_i$ :  $R_{:j}$ :

$$\min_{L,R} f(L,R) = \sum_{(i,j) \in \text{Data}} \left\| X_{ij} - \sum_{k=1}^{K} L_{ik} R_{ik} \right\|^2.$$

(2.1)

This objective function is often optimized with the stochastic gradient descent (SGD) algorithm [35, 55], and the gradient can be calculated as follows:

$$\frac{\partial f}{\partial L_{ik}} = \sum_{(a,b)\in \text{Data}} \delta(a=i) \left[ -2X_{ab}R_{kb} + 2L_{a\cdot}R_{\cdot b}R_{kb} \right]

\frac{\partial f}{\partial R_{kj}} = \sum_{(a,b)\in \text{Data}} \delta(b=j) \left[ -2X_{ab}L_{ak} + 2L_{a\cdot}R_{\cdot b}L_{ak} \right]$$

(2.2)

where f is the objective function in Eq(2.1), and  $\delta(a=i)$  equals 1 if a=i, 0 otherwise.

In every iteration, it computes the gradients  $\frac{\partial f}{\partial L_{ik}}$  and  $\frac{\partial f}{\partial R_{kj}}$ , according to the current model parameter values L and R, and updates the model parameters with the SGD algorithm. It keeps doing that, until the model converges. The MF model can be trained in a data-parallel manner with a parameter server. To do that, we can distribute the data points  $X_{ij}$  evenly over multiple machines, and use the parameter server to manage the shared model parameters L and R. Algorithm 1 shows the basic structure of a data-parallel MF implementation. In each iteration, each worker iterates over all its assigned matrix entries, and reads and updates the parameter data accordingly.

## 2.4.2 Deep learning

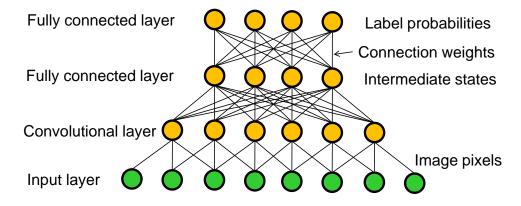

Deep learning is a popular task for learning deep neural network models. In deep learning, the ML programmer/user does not specify which specific features of the raw input data correlate with the outcomes being associated. Instead, the ML algorithm determines which features correlate most strongly by training a *deep neural network* with a large number of hidden layers [6]. A deep neural network, as depicted in Figure 2.4, is a multi-layer network, that encodes the connections between the input (e.g., raw images) and the output (e.g., image labels).

<sup>1</sup>If we partition the X matrix in such a way that each row is assigned to a particular worker, the corresponding L matrix rows can be kept locally by the workers, and only the R matrix needs to be kept in the parameter server.

#### **Algorithm 1** Data-parallel matrix factorization with a parameter server.

```

while not converged do

for each known entry X_{ij} do

Li = ps.Read(i-th row of L matrix)

Rj = ps.Read(j-th row of R matrix)

Compute the gradients LiGrad and RjGrad from Eq(2.2)

Scale the gradients with the learning rate

ps.Update(i-th row of L matrix, LiGrad)

ps.Update(j-th row of R matrix, RjGrad)

end for

ps.Clock()

end while

```

Figure 2.4: A convolutional neural network, with one convolutional layer and two fully connected layers.

Our deep learning benchmarks include two applications, image classification [20, 52, 29, 82] and video classification [31, 94]. An image classification network classifies images (raw pixel maps) into pre-defined labels. Its network is trained with a large set of training images with known labels. The video classification network classifies videos (a sequence of image frames) into pre-defined labels. It often uses an image classification network as a submodule and stacks recurrent layers on it to capture the sequence information. This subsection will describe the image classification application first and then describe how a video classification network can be built on it.

The image classification task often uses a type of model called a convolutional neural network (CNN). The first layer of the nodes (input of the network) are the raw pixels of the input image, and the last layer of the nodes (output of the network) are the probabilities that this image should be assigned to each label. The nodes in the middle are intermediate states. To classify an image with such a neural network, the image pixels will be assigned as the values for the first layer of nodes, and these nodes will activate their connected nodes of the next layer. There is a weight associated with each connection, and the value of each node at the next layer is a prespecified function of the weighted values of its connected nodes. Each layer of nodes is activated, one by one, by the setting of the node values for

the layer below. This procedure is called a forward pass.

There several types of layers. For example, a *fully connected* layer activates its neurons as the weighted sum of all the node values at the prior level. A *convolutional* layer activates its neuron with a convolution function over a (typically small) subset of the node values.

A common way of training a neural network is to use the SGD algorithm. For each training image, a forward pass is done to activate all nodes using the current weights. The values computed for each node are retained as intermediate states. At the last layer, an *error term* is calculated by comparing the predicted label probabilities with the true label. Then, the error terms are propagated back through the network with a *backward pass*. During the backward pass, the gradient of each connection weight is calculated from the error terms and the retained node values, and the connection weights (i.e., the model parameters) are updated using these gradients.

For efficiency, most training applications do each forward and backward pass with a batch of images (called a *mini-batch*) instead of just one image. For each image inside the mini-batch, there will be one set of node activation values during the forward pass and one set of error terms during the backward pass. Convolutional layers tend to have far fewer weights than fully connected layers, both because there are far fewer connections and because, by design, many connections share the same weight.

Video classification tasks often use a structure called a recurrent neural network (RNN). An RNN is made up of multiple layers with recurrent (i.e. feedback) connections, called recurrent layers, such that a static unrolling of the RNN would be a very deep network with shared weights between some of the layers. The Long-Short Term Memory (LSTM) layer [43] is one popular type of recurrent layers that is frequently used for vision and speech tasks to capture sequence information of the data [31, 90, 94]. The LSTM layer contains memory cells that "remember" knowledge of previous timestamps, and the memory is updated selectively at each timestamp, controlled by special gate functions. A common approach for using RNNs on vision tasks, such as video classification [31, 94] and image captioning [90], is to stack LSTM layers on top of CNN layers. The CNN layers serve as an encoder that converts each frame of a video into a feature vector and feeds the video as a sequence of feature vectors into the LSTM layers.

## 2.4.3 Latent Dirichlet allocation (LDA) for topic modeling

LDA is an unsupervised method for discovering hidden semantic structures (topics) in an unstructured collection of documents, each consisting of a bag (multi-set) of words [40]. LDA discovers the topics via word co-occurrence. For example, "Obama" is more likely to co-occur with "Congress" than "super-nova", and thus "Obama" and "Congress" are categorized to the same topic associated with political terms, and "super-nova" to another topic associated with scientific terms. Further, a document with many instances of "Obama" would be assigned a topic distribution that peaks for the politics topics. LDA learns the hidden topics and the documents' associations with those topics jointly. It is often used for news categorization, visual pattern discovery in images, ancestral grouping from genetics data, and community detection in social networks.

The LDA model is often trained with the collapsed Gibbs sampling (CGS) algorithm [40],

which is a type of Markov Chain Monte Carlo (MCMC) method that is used to produce random samples from a probability distribution that would otherwise be difficult to solve analytically.

Formally, let  $w_{ij}$  be the term in the *i*-th document's *j*-th word position, let  $\theta_i$  be document *i*'s *K*-dimensional topic vector, and let  $\beta_{kv}$  be the probability of term *v* occurring in topic  $k \in \{1, \ldots, K\}$ . Finally, let  $z_{ij} \in \{1, \ldots, K\}$  be the (single) topic assigned to  $w_{ij}$ , e.g. "Obama" could be assigned to the "Politics" topic. We are given  $w_{ij}$  as input, and the goal is to find the posterior distribution of  $\theta_i$ ,  $\beta_{kv}$  under the LDA model

$$\prod_{i=1}^{N} \prod_{j=1}^{N_i} \mathbb{P}(w_{ij} \mid z_{ij}, \beta) \mathbb{P}(z_{ij} \mid \theta_i) \mathbb{P}(\theta_i) \mathbb{P}(\beta), \tag{2.3}$$

where  $\mathbb{P}(\theta_i)$ ,  $\mathbb{P}(\beta)$  are prior distributions over  $\theta_i$ ,  $\beta$ . When CGS is applied, the variables  $\theta_i$ ,  $\beta$  are integrated out, leaving  $z_{ij}$  as the only random variables. The  $z_{ij}$  are sampled from the K-category distribution

$$\mathbb{P}(z_{ij} \mid \mathbf{z} \setminus z_{ij}, \mathbf{w}),$$

where  $\mathbf{z} \setminus z_{ij}$  is all other z's apart from  $z_{ij}$ , and  $\mathbf{w}$  is the set of all terms. To compute this distribution, we need to maintain two integer tables as the parameter data, a **document-topic** table and a **word-topic** table that count how many  $z_{ij}$  belong to each (document,topic) pair and each (word,topic) pair respectively.

To implement a data-parallel LDA, we can partition all the documents evenly across multiple worker machines. In every iteration, each worker goes through its assigned documents and makes adjustments to the document-topic table and the word-topic table accordingly. Algorithm 2 shows the basic structure of data-parallel LDA.

### Algorithm 2 Data-parallel LDA with a parameter server.

```

while not converged do

for each word w in document d do

WordTopicVector = ps.Read(w-th row of WordTopicTable)

DocumentTopicVector = ps.Read(d-th row of DocumentTopicTable)

Compute the NewTopic assignment of this word occurrence with CGS

OldTopic ← previous topic assignment

TopicVectorUpdate[NewTopic] = 1

TopicVectorUpdate[OldTopic] = -1

ps.Update(w-th row of WordTopicTable, TopicVectorUpdate)

ps.Update(d-th row of DocumentTopicTable, TopicVectorUpdate)

Store the NewTopic assignment as local state

end for

ps.Clock()

end while

```

#### 2.4.4 PageRank

PageRank is a link analysis algorithm, and it assigns a numerical weighting (i.e., rank) to each node of a hyperlinked set of documents (e.g., pages in the World Wide Web), with the purpose of "measuring" its relative importance within the set [11]. The rank of each node is decided as:

$$Rank(i) = (1-d) + d(\sum_{j \in Neighbor(i)} \frac{Rank(j)}{Degree(j)})$$

(2.4)

where d is a damping factor and is usually set to a constant number of 0.85.

The PageRank algorithm is frequently used as the benchmark application by many graph computing engines, such as GraphLab [60], Pregel [62], GraphX [38], as well as parameter server systems, such as LazyTable [25]. To implement a data-parallel PageRank application with the parameter server model, we can partition the edges of the input graph evenly among all workers and keep the page-ranks in the parameter server. The structure of the PageRank application is shown in Algorithm 3. In every iteration, each worker goes through all edges in its sub-graph and updates the page-rank of the destination node according to the current page-rank of the source node. We repeat this procedure until the model converges.

#### **Algorithm 3** PageRank implementation on a parameter server.

```

while not converged do

for each edge from src to dst do

SrcRank = ps.Read(src)

DstRankContributionFromSrc = d \times \frac{SrcRank}{SrcDegree}

DstRankUpdate = DstRankContributionFromSrc - PrevDstRankContributionFromSrc ps.Update(<math>dst, DstRankUpdate)

Store the new DstRankContributionFromSrc as local state end for ps.Clock()

end while

```

# Chapter 3

# IterStore: Exploiting Iterativeness for Efficient Parallel ML

This chapter explores an opportunity created by the iterative-ness characteristic of the machine learning tasks: knowable repeating patterns of access to the shared state. Often, each ML worker processes its portion of the input data in the same order in each iteration, and the same subset of parameters is read and updated any time a particular data item is processed. So, each iteration involves the same pattern of reads and writes to the shared state.

Knowledge of these patterns can be exploited to improve efficiency, both within a multi-core machine and for communication across machines. For example, within a machine, state used primarily by one thread can be placed in the memory NUMA zone closest to the core on which it runs, while significantly write-shared state can be replicated in thread-private memory to reduce lock contention and synchronized only when required. Naturally, cross-machine overheads can be reduced by appropriate partitioning and prefetching of parameter state. But, one can gain further efficiency by constructing static structures for both the servers' and workers' copies of the shared state, rather than the general dynamic structures that would typically be used, organized according to the prefetch and update batches that will occur each iteration so as to minimize marshaling costs. Indeed, even those batch prefetch and update requests can be constructed statically.

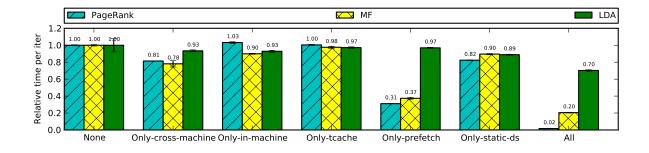

Using three real and oft-studied ML applications (matrix factorization, LDA, and Page-Rank), we experiment extensively with a broad collection of iteration-aware specializations in a parameter server (called IterStore) that was originally designed assuming arbitrary access patterns. Altogether, we find that the specializations reduce per-iteration runtimes by 33–98%. Measuring their individual impacts shows that different specializations are most significant for different ML applications, based on their use of shared state, and that there can be synergistic dependencies among them. For example, informed prefetching is crucial for all of the applications, but must be coupled with static pre-marshaled cache structures to achieve high performance on PageRank.

We also evaluate costs associated with attempting to exploit iterative-ness. Naturally, the work of detecting and processing per-iteration patterns is part of an application's overall execution time. We find that most of the specializations compensate for those costs, though

cross-machine partitioning surprisingly sometimes does not. We also find that, although capturing the patterns during execution of the first iteration does work, it is more efficient if the application instead does an explicit *virtual iteration* that performs the reads and updates without affecting any state. Finally, we find that the benefits of the specializations are robust to imperfect information about the pattern, as might occur when converged values are no longer modified or responsibility for processing some input data items is shifted to another thread.

# 3.1 Background and prior approaches

In prior state-of-art approaches, as is described in Section 2.3, a parameter server system is most similar to a generic distributed key-value store, where the parameter data is stored as a collection of key-indexed rows, managed by a distributed cluster of servers. This design, however, is often an overkill for iterative ML applications. We find many iterative ML applications, including all four applications described in Section 2.4, have the property that the same (or nearly the same) sequence of accesses is applied to the parameter data every iteration, as is illustrated in Figure 3.1. This is because, for these applications, each worker processes its portion of the input data in the same order in each iteration, and the same subset of parameter data is read and updated any time a particular data item is processed. So, each iteration involves the same pattern of reads and writes to the parameter data. We call this property *iterative-ness*.

Figure 3.1: Iterativeness in PageRank. The graph contains three pages and four links. Each of the two workers is assigned with two links. In every iteration, each worker goes through its assigned links. For each link, the worker reads the rank of the source page and updates the rank of the destination page. The same sequence of accesses repeats every iteration.

The iterative-ness property creates an opportunity for efficiency: when per-worker sequences of reads and updates repeat every iteration, they can be known in advance and used to reduce the overheads associated with maintaining the data in the parameter server. The rest of this section will discuss approaches to identifying the sequences and a variety of ways that they can be exploited.

## 3.2 Exploiting iterative-ness for performance

The iterative-ness discussed above creates an opportunity: when per-worker sequences of reads and updates repeat each iteration, they can be known in advance and used to reduce the overheads associated with maintaining the shared state. This section discusses approaches to identifying the sequences and a variety of ways that they can be exploited.

### 3.2.1 Obtaining per-iteration access sequence

There are several ways that a parameter server can obtain the access sequences, with different overheads and degrees of help from the application writer. Of course, an ideal solution would have no overhead and need no help, but realistic options are non-optimal on one or both of these axes.

At one end of the spectrum would be completely transparent detection, in which the parameter server gathers the pattern between pairs of Clock calls. Although this seems straightforward, it is not for two primary reasons. First, many ML applications use the parameter server before beginning to iterate, such as to initialize parameter values appropriately. Because the initialization access pattern likely does not match the periteration pattern, and may involve several calls to Clock, identifying the right pattern would require comparing inter-Clock patterns until a repeat is found. Second, not every iterative ML application is perfectly repetitive, so such a repeat may never be found, either because there are no exact matches or perhaps even no significant repetitiveness at all. Third, exploitation of repeating patterns can only begin after they are known, so a significant portion of the application may be executed inefficiently until then. And, of course, the shared state must be retained in any conversion of the parameter server to a more efficient configuration. These three issues make the fully transparent approach high overhead and not robust; we do not consider it further.

Instead, we explore two options that involve some amount of assistance from the application programmer, illustrated in Figure 3.2: explicit reporting of the sequence (right-most pseudo-code) and explicit reporting of the iteration boundaries (middle pseudo-code). Both options are described in terms of the access sequence being reported once, at the beginning of the application. But, detecting and specializing can be repeated multiple times in an execution, if the access pattern changes dramatically. Section 3.4.6 shows that doing so is unnecessary for moderate access pattern changes.

Explicit virtual iteration. The first, and most efficient, option involves having the application execute what we call a virtual iteration. In a virtual iteration, each application worker reports their sequence of parameter server operations (Read, Update, and Clock) for an iteration. The parameter server logs the operations and returns success, without doing any reads or writes. Naturally, because no real values are involved, the application code cannot have any internal side-effects or modify any state of its own when performing the virtual iteration. So, ideally, the code involved in doing an iteration would be side-effect free (at least optionally) with respect to its local state; our example applications accommodate this need. If the per-iteration code normally updates local state, but still has repeating patterns, then a second side-effect free version of the code would be needed for executing

```

// Gather in virtual iter

// Original

// Gather in first iter

InitParams()

InitParams()

ps.StartGather(virtual)

ps.Clock()

ps.Clock()

DoIteration()

do {

ps.FinishGather()

DoIteration()

if (first iteration)

InitParams()

ps.Clock()

ps.StartGather(real)

ps.Clock()

} while (not stop)

DoIteration()

do {

if (first iteration)

DoIteration()

ps.FinishGather()

ps.Clock()

ps.Clock()

} while (not stop)

} while (not stop)

```